Low Power FPGA Design: Mastering Techniques & Best Practices for Energy-Efficient Hardware

Low Power FPGA Design: Mastering Techniques & Best Practices for Energy-Efficient Hardware

In an era defined by portable devices, IoT proliferation, and edge computing, low power FPGA design stands as a cornerstone of sustainable and efficient digital systems. Integrated circuits in FPGAs—once synonymous with raw performance—now demand intelligent power management to extend battery life, reduce thermal loads, and minimize environmental impact. This article unpacks the essential techniques and best practices that engineers apply to build FPGA systems optimized for minimal power consumption without sacrificing performance.

From architecture-aware synthesis to dynamic voltage and frequency scaling, every layer of design plays a critical role in shaping energy-efficient FPGA deployment.

At the heart of low power FPGA design lies a deep understanding of power sources and their dominant contributors in reconfigurable logic. Unlike ASICs, FPGAs feature inherently higher static power due to constantly active routing and logic blocks, even in idle states.

According to Dr. Elena Petrova, FPGA power optimization expert at Synopsys, “FPGAs consume power not just from active switching, but much more from leakage and overhead in reconfigurable fabrics. Effective design requires targeting these areas holistically.” The greatest gains stem from minimizing unnecessary switching activity while maintaining functional integrity—an objective that guides modern low power strategies across all stages of FPGA development.

Optimizing the Core: Design Architecture & Power Efficiency

The architecture chosen for an FPGA implementation directly influences its power profile. Designers must carefully evaluate resource utilization, logic depth, and logic family properties before synthesis. Low power FPGA projects often favor architectures with reduced parasitic capacitance and optimized switching activity.For example, using compact routing resources instead of long trace-heavy paths lowers both dynamic and static power. Tools such as Xilinx Vivado and Intel Quartus offer power-aware innovation in place and route optimization. These platforms employ algorithms that minimize short-circuit currents and reduce clutter by preferring direct connections where feasible.

*Magic Synthesis Directed Placement and Routing (MS-DPR)*, introduced in recent tool generations, intelligently maps critical paths to low-leakage regions of the FPGA fabric, shrinking both energy and timing variance. An effective architectural approach involves partitioning the design into functional blocks with distinct power modes. “By segmenting the system into duty-cycled components—such as processing units operating only during active cycles—total power demand drops significantly,” explains Marcus Lin, FPGA power architect at Microchip Technology.

This modular strategy, combined with apt clock domain management, prevents wasteful continuous operation across the entire board.

Power-Aware Synthesis and Clock Management

Synthesis tools have evolved to incorporate power estimation and enforcement during logic optimization. Key techniques include minimizing switching activity through logic restructuring—such as using shared multipliers over redundant instances—and prioritizing low-power primitives embedded in FPGA vendors’ logic libraries.For instance, gate-level optimizations tailor primitive shifts and multipliers to versions with lower switching capacitance. Clock management stands as one of the most influential levers in power saving. The famous overhead from global clock networks can consume up to 30% of total FPGA power in large designs.

To counter this: - Dynamic clock scaling adjusts frequency per functional block based on workload intensity. - Clock gating disables clock signals to idle modules, instantly reducing dynamic power. - Merging clock domains where possible cuts unnecessary switching transitions.

Real-world deployment of these mechanisms requires precise control via built-in PMICs (Power Management Integrated Circuits) and license-gated clock sets, enabling fine-grained power shutdown of peripheral subsystems.

Power Gating & submission of Low-Power States

Modern FPGAs feature programmable power islands and register sets designed specifically for deep low-power operation. Leveraging these capabilities, designers implement power gating—de-energizing entire blocks or regions of the design when not in use—to reduce static leakage.This technique is particularly valuable in always-on applications where certain subsystems remain idle. Tools support structured approaches to power gating through hierarchical power domains defined in design flows. For example, IP blocks can be tagged with power entry points via Intel’s MS-PGSDK or Xilinx’s Power Shrink plugin, enabling automated insertion of enable switch logic.

Successful power gating also depends on robust power-aware simulation and validation; transient voltage drops must be managed to prevent soft errors or functional glitches. Power-aware firmware integrates seamlessly by triggering sleep states based on system events—such as network packet arrival or sensor read intervals—ensuring no residual power drain during inactivity periods.

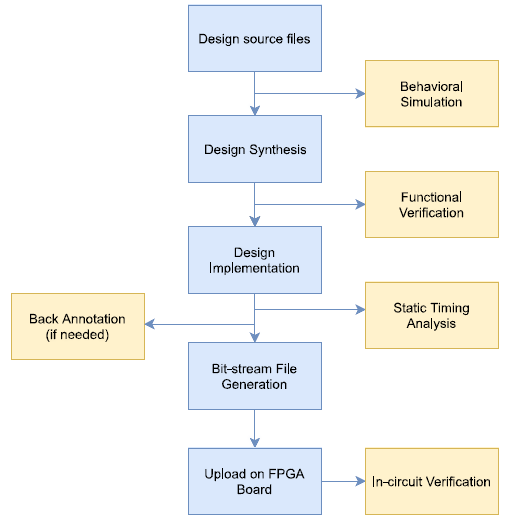

Flow-Driven Optimization: Power Is in the Workflow

Low power FPGA design is not isolated to hardware; development methodology and workflow choices profoundly influence energy efficiency.Adopting a top-down, modular design process with iterative profiling allows early identification of power hotspots. Engineers recommend: - Profiling tooling from vendors to measure per-module power directly during synthesis and synthesis-simulation. - Early incorporation of thermal and power constraints within hardware description languages (HDLs) using coverage-driven quality attributes.

- Using power-preserving coding patterns, such as avoiding excessive state toggling and favoring combinational over sequential logic in short-path designs. Moreover, leveraging vendor-specific low-power IP cores—like Xilinx PowerEst or Intel’s PowerPlay rollback provisions—provides ready-to-use optimization building blocks. These IPs automate cost-effective decisions without compromising design flexibility, accelerating time-to-energy-efficient solutions.

Real-World Impact: From Design to Deployment

In practical deployment, low power FPGA designs transform consumer electronics, autonomous vehicles, and industrial automation. Wearables extending battery life by years, drones with longer flight durations, and smart sensors operating on harvests—all rely on FPGA strategies that balance performance and power. Take edge AI inference, where FPGA acceleration demands careful partitioning between high-throughput cores and latency-sensitive control paths.By assigning the inference engine to a low-leakage region and controlling clock frequency dynamically, power consumption can remain below 2W—crucial for battery-limited systems. This approach exemplifies how low power FPGA design is no longer optional but essential for modern deployment constraints.

Ultimately, low power FPGA design is a multidisciplinary challenge rewarding both architectural insight and meticulous implementation.From strategic partitioning and clock-aware scheduling to power-aware synthesis and hierarchical gating, each decision compounds into meaningful energy savings. As devices continue shrinking in size yet growing in function, mastering these techniques becomes not just advantageous—but indispensable. The future of sustainable, high-performance FPGA systems hinges on embracing power as a first-class design constraint.

Related Post

Exploring The Serenity Of Anne Hathaway Calma

Boly4u: Decoding the Future of Digital Innovation with a Single Platform

Unlock Instant Rewards: How Block Strike Promo Codes Deliver Free Incentives—Now!

Erin Olash: The Rising Star Reshaping Modern Education